MAX1945R/MAX1945S

### 19-2640; Rev 1; 7/04 EVALUATION KIT AVAILABLE 1MHz, 1% Accurate, 6A Internal Switch Step-Down Regulators

## **General Description**

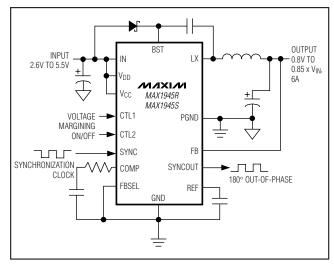

The MAX1945R/MAX1945S high-efficiency pulse-width modulation (PWM) switching regulators deliver up to 6A of output current. The devices operate from an input supply range of 2.6V to 5.5V and provide selectable output voltages of 1.8V, 2.5V, and adjustable output voltages from 0.8V to 85% of the supply voltage. With V<sub>CC</sub> at 3.3V/5V, the input voltage can be as low as 2.25V. The MAX1945R/MAX1945S are ideal for onboard post-regulation applications. Total output voltage error is less than  $\pm$ 1% over load, line, and temperature.

The MAX1945R/MAX1945S operate at a selectable fixed frequency (500kHz or 1MHz) or can be synchronized to an external clock (400kHz to 1.2MHz). The high operating frequency minimizes the size of external components. The high bandwidth of the internal error amplifier provides excellent transient response. The MAX1945R/MAX1945S have internal dual N-channel MOSFETs to lower heat dissipation at heavy loads. Two MAX1945R/MAX1945Ss can operate 180 degrees out-of-phase of each other to minimize input capacitance. The devices provide output voltage margining for board-level testing. The MAX1945R provides a  $\pm 4\%$  voltage margining. The MAX1945S provides a  $\pm 9\%$  voltage margining.

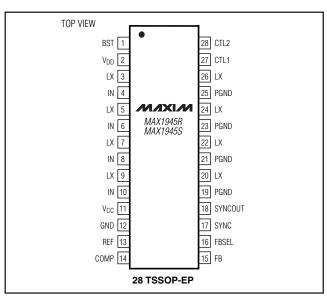

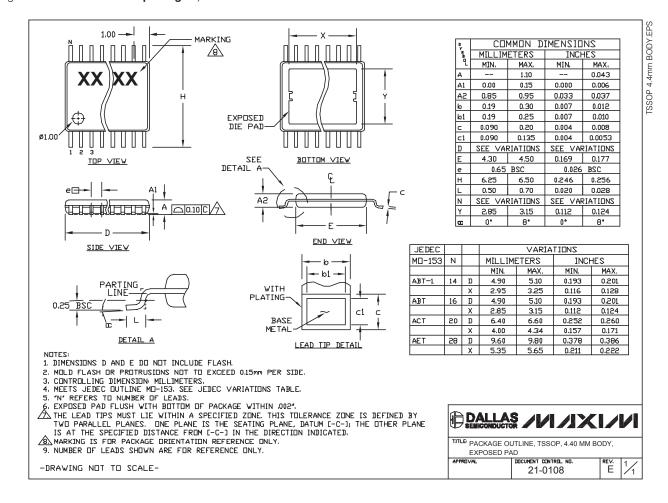

The MAX1945R/MAX1945S are available in 28-pin TSSOP-EP packages and are specified over the -40°C to +85°C industrial temperature range. An evaluation kit is available to speed designs.

### Applications

Low-Voltage, High-Density Distributed Power Supplies

ASIC, CPU, and DSP Core Voltages

RAM Power Supply

Base Station, Telecom, and Networking

Equipment Power Supplies

Server and Notebook Power Supplies

Pin Configuration appears at end of data sheet.

#### **Features**

- 6A PWM Step-Down Regulator with 95% Efficiency

- 1MHz/500kHz Switching for Small External Components

- 0.76in<sup>2</sup> Complete 6A Regulator Footprint

- External Components' Height <3mm</p>

- ±1% Output Accuracy over Load, Line, and Temperature

- Operate from 2.6V to 5.5V Supply

- Operate from 2.5V Input with V<sub>CC</sub> at 3.3V/5V

- Preset Output Voltage of 1.8V or 2.5V

- ♦ Adjustable Output from 0.8V to 85% of Input

- Voltage Margining: ±4% (MAX1945R) or ±9% (MAX1945S)

- Synchronize to External Clock

- SYNCOUT Provides 180-Degree Out-of-Phase Clock Output

- All-Ceramic or Electrolytic Capacitor Designs

Ordering Information

| PART        | TEMP RANGE     | PIN-PACKAGE  |  |  |

|-------------|----------------|--------------|--|--|

| MAX1945REUI | -40°C to +85°C | 28 TSSOP-EP* |  |  |

| MAX1945SEUI | -40°C to +85°C | 28 TSSOP-EP* |  |  |

\*EP = Exposed pad.

# **Typical Operating Circuit**

###

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

### **ABSOLUTE MAXIMUM RATINGS**

CTL1, CTL2, IN, SYNC,  $V_{CC}, V_{DD}$  to GND .....-0.3V to +6V SYNCOUT, COMP, FB, FBSEL,

| REF to GND          | 0.3V to (V <sub>CC</sub> + 0.3V) |

|---------------------|----------------------------------|

| LX Current (Note 1) | 9A to +9A                        |

| BST to LX           | 0.3V to +6V                      |

| PGND to GND         | 0.3V to +0.3V                    |

Continuous Power Dissipation ( $T_A = +85^{\circ}C$ )

| (derate 23.8mW/°C above +70°C)    | 1191mW         |

|-----------------------------------|----------------|

| Operating Temperature Range       | 40°C to +85°C  |

| Storage Temperature Range         | 65°C to +150°C |

| Lead Temperature (soldering, 10s) | +300°C         |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Note 1:** LX has internal clamp diodes to PGND and IN. Applications that forward bias these diodes should take care not to exceed the IC's package power dissipation limits.

### **ELECTRICAL CHARACTERISTICS**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at +25°C.)

| PARAMETER                                              | SYMBOL                      | CONDITIO                                                                        | ONS                            | MIN  | ТҮР  | MAX  | UNITS |

|--------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------|--------------------------------|------|------|------|-------|

| IN/V <sub>CC</sub>                                     |                             | ·                                                                               |                                |      |      |      |       |

| Input Voltage                                          | VIN                         |                                                                                 |                                | 2.6  |      | 5.5  | V     |

| IN Supply Current                                      | lu i                        | SYNC = $V_{CC}$ (1MHz),                                                         | $V_{IN} = 3.3V$                |      | 12   | 20   | m ^   |

| IN Supply Current                                      | lin                         | no load                                                                         | $V_{IN} = 5.5V$                |      | 48   |      | mA    |

| Vac Supply Current                                     | loo                         | $SYNC = V_{CO}(1MH_{7})$                                                        | $V_{CC} = 3.3V$                |      | 2    | 3    | mA    |

| V <sub>CC</sub> Supply Current                         | Icc                         | $SYNC = V_{CC} (1MHz)$                                                          | $V_{CC} = 5.5V$                |      | 3    |      | ША    |

| V <sub>DD</sub> Supply Current                         |                             | SYNC = $V_{CC}$ (1MHz)                                                          | $V_{DD} = 3.3V$                |      | 5    | 8    | mA    |

| VDD Supply Current                                     | IDD                         | STINC = VCC(TIVITZ)                                                             | $V_{DD} = 5.5V$                |      | 10   |      | ША    |

| Total Shutdown Current from IN, $V_{CC},$ and $V_{DD}$ | ITOTAL                      | $V_{IN} = V_{CC} = V_{DD} = V_{BST}$<br>CTL1 = CTL2 = GND                       | - V <sub>LX</sub> = 5.5V,      |      |      | 500  | μA    |

| V <sub>CC</sub> Undervoltage Lockout                   |                             | When LX starts/stops                                                            | V <sub>CC</sub> rising         |      | 2.40 | 2.55 | N/    |

| Threshold                                              | Vuvlo                       | switching                                                                       | V <sub>CC</sub> falling        | 2.20 | 2.35 |      | V     |

| V <sub>DD</sub>                                        |                             |                                                                                 |                                |      |      |      |       |

| V <sub>DD</sub> Shutdown Supply Current                |                             | $V_{IN} = V_{DD} = V_{BST} = 5.5V$ , $V_{LX} = 5.5V$ or 0,<br>CTL1 = CTL2 = GND |                                |      |      | 10   | μA    |

| BST                                                    |                             |                                                                                 |                                |      |      |      | 1     |

| BST Shutdown Supply Current                            | I <sub>BST</sub>            | $V_{IN} = V_{DD} = V_{BST} = 5.5V$<br>CTL1 = CTL2 = GND                         | $V_{LX} = 5.5V \text{ or } 0,$ |      |      | 10   | μA    |

| REF                                                    |                             |                                                                                 |                                |      |      |      |       |

| REF Voltage                                            | VREF                        | $I_{REF} = 0, V_{IN} = 2.6V \text{ to } 5.8$                                    | ōV                             | 1.97 | 2.00 | 2.04 | V     |

| REF Shutdown Resistance                                |                             | From REF to GND, CTL1                                                           | = CTL2 = GND                   |      | 10   | 100  | Ω     |

| COMP                                                   |                             |                                                                                 |                                |      |      |      |       |

|                                                        |                             |                                                                                 | FBSEL = High-Z                 | 30   | 55   | 85   |       |

| COMP Transconductance                                  |                             | From FB to COMP,<br>$V_{COMP} = 1.25V$                                          | FBSEL = GND                    | 13.3 | 24.4 | 37.8 | μS    |

|                                                        |                             | VCOMP = 1.25V                                                                   | $FBSEL = V_{CC}$               | 9.6  | 17.6 | 27.2 |       |

| COMP Clamp Voltage Low                                 | V <sub>LOW</sub> _<br>CLAMP | V <sub>IN</sub> = 2.6V to 5.5V, V <sub>FB</sub> = 0.9V                          |                                | 0.5  | 0.8  | 1.1  | V     |

| COMP Clamp Voltage High                                | Vhigh_<br>clamp             | $V_{IN} = 2.6V$ to 5.5V, $V_{FB} = 0.7V$                                        |                                | 1.90 | 2.15 | 2.40 | V     |

| COMP Shutdown Resistance                               |                             | From COMP to GND, CTL                                                           | _1 = CTL2 = GND                |      | 10   | 100  | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at +25°C.)

| PARAMETER                                 | SYMBOL          | CONDITIONS                                                                              |                                                                                                         | MIN   | ТҮР   | MAX   | UNITS |

|-------------------------------------------|-----------------|-----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| FB                                        | •               |                                                                                         |                                                                                                         |       |       |       |       |

|                                           |                 |                                                                                         | FBSEL = GND                                                                                             | 1.782 | 1.800 | 1.818 |       |

| FB Regulation Voltage<br>(Error Amp Only) | V <sub>FB</sub> | $V_{COMP} = 1V \text{ to } 2V,$<br>$V_{IN} = 2.6V \text{ to } 5.5V$                     | $FBSEL = V_{CC}$                                                                                        | 2.475 | 2.500 | 2.525 | V     |

|                                           |                 | VIN = 2.0V to 3.3V                                                                      | FBSEL = High-Z                                                                                          | 0.792 | 0.800 | 0.808 |       |

| Maximum Output Current                    | IFB_OUT         | $V_{IN} = 3.3V, V_{OUT} = 1.8V$                                                         | , L = 1μH                                                                                               | 6     |       |       | А     |

|                                           |                 |                                                                                         | $\begin{array}{l} \text{CTL1} = \text{V}_{\text{CC}},\\ \text{CTL2} = \text{V}_{\text{CC}} \end{array}$ | -1    |       | +1    |       |

|                                           |                 | MAX1945R,<br>$V_{COMP} = 1V \text{ to } 2V,$<br>$V_{IN} = 2.6V \text{ to } 5.5V$        | $\begin{array}{l} \text{CTL1} = \text{GND},\\ \text{CTL2} = \text{V}_{\text{CC}} \end{array}$           | 3     |       | 5     |       |

| FB Voltage Margining Output               |                 |                                                                                         | $CTL1 = V_{CC},$<br>CTL2 = GND                                                                          | -5    |       | -3    | %     |

| (Error Amp Only)                          | Vmargin_        |                                                                                         | $CTL1 = V_{CC},$<br>$CTL2 = V_{CC}$                                                                     | -1    |       | +1    | 70    |

|                                           |                 | MAX1945S,<br>V <sub>COMP</sub> = 1V to 2V,<br>V <sub>IN</sub> = 2.6V to 5.5V            | $\begin{array}{l} \text{CTL1} = \text{GND},\\ \text{CTL2} = \text{V}_{\text{CC}} \end{array}$           | 8     |       | 10    |       |

|                                           |                 |                                                                                         | $CTL1 = V_{CC},$<br>CTL2 = GND                                                                          | -10   |       | -8    |       |

| FB Input Resistance                       |                 | FB to GND, FBSEL = GND, or $V_{FB}$ = 1.8V,<br>or FBSEL = $V_{CC}$ , or $V_{FB}$ = 2.5V |                                                                                                         | 25    | 50    | 100   | kΩ    |

| FB Input Bias Current                     |                 | $FBSEL = High-Z, V_{FB} =$                                                              | 0.7V                                                                                                    |       | 0.01  | 0.10  | μΑ    |

| LX                                        |                 |                                                                                         |                                                                                                         |       |       |       |       |

| LX On-Resistance High                     | RON_HIGH_       | $V_{IN} = V_{BST} - V_{LX} = 3.3V$                                                      |                                                                                                         |       | 26    | 43    | mΩ    |

| LA OII-NESISIANCE HIGH                    | LX              | $V_{IN} = V_{BST} - V_{LX} = 2.6V$                                                      |                                                                                                         |       | 30    | 50    | 11152 |

| LX On-Resistance Low                      | RON_LOW_        | $V_{IN} = 3.3V$                                                                         |                                                                                                         |       | 26    | 43    | mΩ    |

|                                           | LX              | V <sub>IN</sub> = 2.6V                                                                  |                                                                                                         |       | 30    | 50    | 11122 |

| LX Current-Sense<br>Transresistance       |                 | From LX to COMP                                                                         |                                                                                                         | 43    | 54    | 65    | mΩ    |

| LX Current-Limit Threshold                |                 | Duty cycle =100%,                                                                       | High side                                                                                               | 8.0   | 10.4  | 12.8  | ^     |

|                                           |                 | V <sub>IN</sub> = 2.6V/3.3V/5.5V                                                        | Low side                                                                                                | -6    | -4    | -2    | A     |

| LX Leakage Current                        |                 | V <sub>IN</sub> = 5.5V,                                                                 | $V_{LX} = 5.5V$                                                                                         |       |       | 100   | μA    |

| En Loanage Ourrent                        | ILEAK_LX        | CTL1 = CTL2 = GND                                                                       | LX = GND                                                                                                | -100  |       |       | μΑ    |

| LX Switching Frequency                    | fsw             | $V_{IN} = 2.6V/3.3V$                                                                    | $SYNC = V_{CC}$                                                                                         | 0.8   | 1.0   | 1.2   | MHz   |

|                                           | 1300            | VIIN - 2.0 V/0.0 V                                                                      | SYNC = GND                                                                                              | 400   | 500   | 600   | kHz   |

| LX Minimum Off-Time                       | tOFF            | $V_{IN} = 2.6V/3.3V$                                                                    |                                                                                                         |       | 155   | 180   | ns    |

| LX Maximum Duty Cycle                     |                 | $V_{IN} = 2.6V/3.3V$                                                                    | SYNC = GND                                                                                              | 90    |       |       | %     |

| Extracting Daty Oyolo                     |                 | VIN = 2.0V/3.3V                                                                         | SYNC = $V_{CC}$                                                                                         | 80    |       |       | /0    |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at +25°C.)

| PARAMETER                       | SYMBOL                           | CONDITIC                                                 | INS             | MIN                       | ТҮР                       | MAX                       | UNITS |

|---------------------------------|----------------------------------|----------------------------------------------------------|-----------------|---------------------------|---------------------------|---------------------------|-------|

|                                 |                                  |                                                          | SYNC = GND      |                           | 8.8                       | 10.5                      | 0/    |

| LX Minimum Duty Cycle           |                                  | $V_{IN} = 2.6V/3.3V$                                     | SYNC = $V_{CC}$ |                           | 17.6                      |                           | %     |

| RMS LX Output Current           |                                  |                                                          |                 |                           |                           | 6                         | Α     |

| FBSEL                           |                                  |                                                          |                 |                           |                           |                           |       |

| FBSEL Input Threshold 1.8V      |                                  | Where 1.8V feedback switches in and out,                 | FBSEL rising    |                           | 0.16                      | 0.22                      | v     |

|                                 |                                  | $V_{\rm CC} = 2.6 \text{V}/3.3 \text{V}/5.5 \text{V}$    | FBSEL falling   | 0.08                      | 0.14                      |                           |       |

|                                 |                                  | Where 2.5V feedback                                      | FBSEL rising    |                           | V <sub>CC</sub> -<br>0.14 | V <sub>CC</sub> -<br>0.08 |       |

| FBSEL Input Threshold 2.5V      |                                  | switches in and out,<br>V <sub>CC</sub> = 2.6V/3.3V/5.5V | FBSEL falling   | V <sub>CC</sub> -<br>0.22 | V <sub>CC</sub> -<br>0.16 |                           | V     |

| FBSEL Input Current Low         | ILOW_<br>FBSEL                   | FBSEL = GND                                              |                 | -50                       | -20                       |                           | μA    |

| FBSEL Input Current High        | IHIGH_<br>FBSEL                  | FBSEL = V <sub>CC</sub>                                  |                 |                           | 20                        | 50                        | μA    |

| CTL1 /CTL2                      | •                                |                                                          |                 |                           |                           |                           |       |

| CTL1/CTL2 Input Threshold       | VIL_CTL_                         | $V_{IN} = 2.6V \text{ to } 5.5V$                         |                 | 0.4                       | 0.95                      |                           | V     |

|                                 | VIH_CTL_                         |                                                          |                 |                           | 1.0                       | 1.6                       | -     |

| CTL1/CTL2 Input Current         | IIL_CTL_                         | $V_{CTL1}$ or $V_{CTL2} = 0$ or 5.5V, $V_{IN} = 5.5V$    |                 | -1<br>-1                  |                           | +1<br>+1                  | μA    |

| Soft-Start Period               |                                  | Time required for output to                              | o ramp up       | 2.9                       | 3.7                       | 4.5                       | ms    |

| Time from Nominal to Margin     | tHIGH_4%                         | +4%                                                      |                 |                           | 160                       |                           |       |

| High                            | thigh_9%                         | +9%                                                      |                 |                           | 360                       |                           | μs    |

| Time from Nominal to Marcin Low | tLOW_4%                          | -4%                                                      |                 |                           | 450                       |                           |       |

| Time from Nominal to Margin Low | tLOW_9%                          | -9%                                                      |                 |                           | 1000                      |                           | μs    |

| SYNC                            | -                                |                                                          |                 | -                         |                           |                           | -     |

| SYNC Capture Range              |                                  | $V_{IN} = 2.6V \text{ to } 5.5V$                         |                 | 0.4                       |                           | 1.2                       | MHz   |

| SYNC Pulse Width                | t <sub>LO,</sub> t <sub>HI</sub> | $V_{IN} = 2.6V$ to 5.5V                                  |                 | 250                       |                           |                           | ns    |

| SVNC Input Throobold            | VIL_SYNC                         | $V_{\rm INI} = 2.6 V/to 5.5 V/$                          |                 | 0.40                      | 0.95                      |                           | V     |

| SYNC Input Threshold            | VIH_SYNC                         | $V_{IN} = 2.6V \text{ to } 5.5V$                         |                 |                           | 1.0                       | 1.6                       | V     |

| SYNC Input Current              | I <sub>IL,</sub> I <sub>IH</sub> | $V_{SYNC} = 0 \text{ or } 5.5V, V_{IN} = 3$              | 5.5V            | -1                        |                           | +1                        | μA    |

| SYNCOUT                         |                                  |                                                          |                 |                           |                           |                           |       |

| SYNCOUT Frequency Range         | <b>f</b> SYNCOUT                 | $V_{CC} = 2.6V$ to 5.5V                                  |                 | 0.4                       |                           | 1.2                       | MHz   |

| SYNCOUT Output Voltage          | V <sub>OH_SYNC</sub><br>OUT      | ISYNCOUT = ±1mA, Vcc =                                   | 2 6V/ to 5 5V   | V <sub>CC</sub> -<br>0.4  | V <sub>CC</sub> -<br>0.05 |                           | v     |

| Smooor Supul Vollage            | VOL_SYNC<br>OUT                  | $\frac{1}{10000000000000000000000000000000000$           | 2.00 10 0.00    |                           | 0.05                      | 0.40                      | v     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F, **T<sub>A</sub> = 0°C to +85°C**, unless otherwise noted. Typical values are at +25°C.)

| PARAMETER                   | SYMBOL | CONDITIONS              | MIN | ТҮР | МАХ | UNITS |

|-----------------------------|--------|-------------------------|-----|-----|-----|-------|

| THERMAL SHUTDOWN            |        |                         |     |     |     |       |

| Thermal-Shutdown Hysteresis |        |                         |     | 20  |     | °C    |

| Thermal-Shutdown Threshold  |        | When LX stops switching |     | 165 |     | °C    |

# **ELECTRICAL CHARACTERISTICS**

(V<sub>IN</sub> = V<sub>CC</sub> = V<sub>CTL1</sub> = V<sub>CTL2</sub> = V<sub>DD</sub> = 3.3V, SYNC = GND, FBSEL = High-Z, V<sub>FB</sub> = 0.7V, C<sub>REF</sub> =  $0.22\mu$ F, **T<sub>A</sub>** = -40°C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                                               | SYMBOL                      | CONDITIC                                                                        | INS                            | MIN  | ТҮР | MAX                 | UNITS |

|---------------------------------------------------------|-----------------------------|---------------------------------------------------------------------------------|--------------------------------|------|-----|---------------------|-------|

| IN/V <sub>CC</sub>                                      |                             |                                                                                 |                                |      |     |                     |       |

| Input Voltage                                           | VIN                         |                                                                                 |                                | 2.6  |     | 5.5                 | V     |

| IN Supply Current                                       | l <sub>IN</sub>             | SYNC = V <sub>CC</sub> (1MHz),<br>no load                                       | $V_{IN} = 3.3V$                |      |     | 20                  | mA    |

| V <sub>CC</sub> Supply Current                          | Icc                         | SYNC = $V_{CC}$ (1MHz)                                                          | $V_{CC} = 3.3V$                |      |     | 4                   | mA    |

| V <sub>DD</sub> Supply Current                          | IDD                         | SYNC = $V_{CC}$ (1MHz)                                                          | $V_{DD} = 3.3V$                |      |     | 8                   | mA    |

| Total Shutdown Current from IN, $V_{CC}$ , and $V_{DD}$ | ITOTAL                      | $V_{IN} = V_{CC} = V_{DD} = V_{BST} - CTL1 = CTL2 = GND$                        | $V_{LX} = 5.5V,$               |      |     | 500                 | μA    |

| V <sub>CC</sub> Undervoltage Lockout                    |                             | When LX starts/stops                                                            | V <sub>CC</sub> rising         |      |     | 2.55                |       |

| Threshold                                               | VUVLO                       | switching                                                                       | V <sub>CC</sub> falling        | 2.20 |     |                     | V     |

| V <sub>DD</sub>                                         |                             |                                                                                 |                                |      |     |                     |       |

| V <sub>DD</sub> Shutdown Supply Current                 | IVDD                        | $V_{IN} = V_{DD} = V_{BST} = 5.5V$ , $V_{LX} = 5.5V$ or 0,<br>CTL1 = CTL2 = GND |                                |      |     | 10                  | μA    |

| BST                                                     |                             | ·                                                                               |                                |      |     |                     |       |

| BST Shutdown Supply Current                             | I <sub>BST</sub>            | $V_{IN} = V_{DD} = V_{BST} = 5.5V,$<br>CTL1 = CTL2 = GND                        | $V_{LX} = 5.5V \text{ or } 0,$ |      |     | 10                  | μA    |

| REF                                                     | •                           |                                                                                 |                                |      |     |                     |       |

| REF Voltage                                             | VREF                        | I <sub>REF</sub> = 0, V <sub>IN</sub> = 2.6V to 5.5                             | V                              | 1.96 |     | 2.04                | V     |

| REF Shutdown Resistance                                 |                             | From REF to GND, CTL1 =                                                         | = CTL2 = GND                   |      |     | 100                 | Ω     |

| СОМР                                                    |                             |                                                                                 |                                |      |     |                     |       |

|                                                         |                             |                                                                                 | FBSEL = High-Z                 | 30   |     | 85                  |       |

| COMP Transconductance                                   |                             | From FB to COMP,<br>$V_{COMP} = 1.25V$                                          | FBSEL = GND                    | 13.3 |     | 37.8 μ <sup>(</sup> | μS    |

|                                                         |                             |                                                                                 | $FBSEL = V_{CC}$               | 9.6  |     | 27.2                |       |

| COMP Clamp Voltage Low                                  | V <sub>LOW</sub> _<br>CLAMP | $V_{IN} = 2.6V$ to 5.5V, $V_{FB} = 0.9V$                                        |                                | 0.5  |     | 1.1                 | V     |

| COMP Clamp Voltage High                                 | Vhigh_<br>Clamp             | $V_{IN} = 2.6V$ to 5.5V, $V_{FB} = 0.7V$                                        |                                | 1.90 |     | 2.40                | V     |

| COMP Shutdown Resistance                                |                             | From COMP to GND, CTL                                                           | 1 = CTL2 = GND                 |      |     | 100                 | Ω     |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F, **T<sub>A</sub> = -40°C to +85°C**, unless otherwise noted.) (Note 2)

| PARAMETER                                 | SYMBOL            | CONDITIONS                                                            |                                                                                               | MIN   | TYP M | X UN  | IITS    |

|-------------------------------------------|-------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------|-------|-------|---------|

| FB                                        |                   |                                                                       |                                                                                               |       |       | ľ     |         |

|                                           |                   |                                                                       | FBSEL = GND                                                                                   | 1.773 | 1.8   | 27    |         |

| FB Regulation Voltage<br>(Error Amp Only) | V <sub>FB</sub>   | $V_{COMP} = 1V \text{ to } 2V,$<br>$V_{IN} = 2.6V \text{ to } 5.5V$   | $FBSEL = V_{CC}$                                                                              | 2.462 | 2.5   | 38 \  | V       |

|                                           |                   | VIN - 2.0V 10 0.0V                                                    | FBSEL = High-Z                                                                                | 0.788 | 8.0   | 12    |         |

| Maximum Output Current                    | IFB_OUT           | $V_{IN} = 3.3V, V_{OUT} = 1.8V,$                                      | L = 1µH                                                                                       | 6     |       | A     | A       |

|                                           |                   |                                                                       | $CTL1 = V_{CC},$<br>$CTL2 = V_{CC}$                                                           | -1.5  | +1    | .5    |         |

|                                           |                   | MAX1945R,<br>V <sub>COMP</sub> = 1V to 2V,<br>$V_{IN} = 2.6V$ to 5.5V | CTL1 = GND,<br>$CTL2 = V_{CC}$                                                                | 2.5   | 5.    | 5     |         |

| FB Voltage Margining Output               |                   |                                                                       | $\begin{array}{l} \text{CTL1} = \text{V}_{\text{CC}},\\ \text{CTL2} = \text{GND} \end{array}$ | -5.5  | -2    | -     | %       |

| (Error Amp Only)                          | Vmargin_          |                                                                       | $CTL1 = V_{CC},$<br>$CTL2 = V_{CC}$                                                           | -1.5  | +1    |       | /0      |

|                                           |                   | MAX1945S,<br>V <sub>COMP</sub> = 1V to 2V,<br>$V_{IN} = 2.6V$ to 5.5V | CTL1 = GND,<br>$CTL2 = V_{CC}$                                                                | 7.5   | 10    | .5    |         |

|                                           |                   |                                                                       | $CTL1 = V_{CC},$<br>CTL2 = GND                                                                | -10.5 | -7    | .5    |         |

| FB Input Resistance                       |                   | FB to GND, FBSEL = GNI<br>or FBSEL = $V_{CC}$ , or $V_{FB}$ =         |                                                                                               | 25    | 10    | 10 k  | Ω       |

| FB Input Bias Current                     |                   | FBSEL = High-Z, $V_{FB} = 0$                                          | .7V                                                                                           |       | 0.    | 1 µ   | A       |

| LX                                        |                   |                                                                       |                                                                                               |       |       |       |         |

| LV On Basistanaa High                     | R <sub>ON</sub> _ | $V_{\rm IN} = V_{\rm BST} - V_{\rm LX} = 3.3 V$                       |                                                                                               |       | 4     | 3     | ıΩ      |

| LX On-Resistance High                     | HIGH_LX           | $V_{IN} = V_{BST} - V_{LX} = 2.6V$                                    |                                                                                               |       | 5     | C     | 122     |

|                                           | Ron               | V <sub>IN</sub> = 3.3V                                                |                                                                                               |       | 4     | 3     | -0      |

| LX On-Resistance Low                      | LOW_LX            | V <sub>IN</sub> = 2.6V                                                |                                                                                               |       | 5     | C     | nΩ      |

| LX Current-Sense<br>Transresistance       |                   | From LX to COMP                                                       |                                                                                               | 43    | 6     | 5 m   | nΩ      |

| LX Current Limit Threshold                |                   | Duty cycle =100%,                                                     | High side                                                                                     | 8.0   | 12    | .8    | ^       |

| LX Current-Limit Threshold                |                   | $V_{IN} = 2.6V/3.3V/5.5V$                                             | Low side                                                                                      | -6    | -2    | 2     | A       |

| LX Leakage Current                        | h =               | $V_{IN} = 5.5V,$                                                      | $V_{LX} = 5.5V$                                                                               |       | 1(    |       | . ^     |

| LA Leakage Guirent                        | ILEAK_LX          | CTL1 = CTL2 = GND                                                     | LX = GND                                                                                      | -100  |       | μ     | A       |

| LX Switching Frequency                    | four              | $V_{IN} = 2.6V/3.3V$                                                  | SYNC = $V_{CC}$                                                                               | 0.8   | 1.    | 2 MI  | Hz      |

|                                           | fsw               | VIN = 2.00/3.3V                                                       | SYNC = GND                                                                                    | 400   | 60    | 10 kH | Hz      |

| LX Minimum Off-Time                       | toff              | $V_{IN} = 2.6V/3.3V$                                                  |                                                                                               |       | 18    | 10 n  | าร      |

| LX Maximum Duty Cycle                     |                   | V <sub>IN</sub> = 2.6V/3.3V                                           | SYNC = GND                                                                                    | 90    |       | 0     | <u></u> |

| LA MAXIMUM DULY CYCIE                     |                   | VIN - 2.0V/3.3V                                                       | SYNC = $V_{CC}$                                                                               | 80    |       | ~ %   |         |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{IN} = V_{CC} = V_{CTL1} = V_{CTL2} = V_{DD} = 3.3V$ , SYNC = GND, FBSEL = High-Z,  $V_{FB} = 0.7V$ ,  $C_{REF} = 0.22\mu$ F,  $T_A = -40^{\circ}$ C to +85°C, unless otherwise noted.) (Note 2)

| PARAMETER                            | SYMBOL                           | CONDITIC                                                                                                       | DNS            | MIN                       | ТҮР | MAX                       | UNITS |

|--------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------|----------------|---------------------------|-----|---------------------------|-------|

| LX Minimum Duty Cycle                |                                  | $\begin{array}{l} \text{SYNC} = \text{GND}, \\ \text{V}_{\text{IN}} = 2.6 \text{V} / 3.3 \text{V} \end{array}$ |                |                           |     | 10.5                      | %     |

| FBSEL                                | -                                |                                                                                                                |                | -                         |     |                           |       |

|                                      |                                  | Where 1.8V feedback                                                                                            | FBSEL rising   |                           |     | 0.22                      |       |

| FBSEL Input Threshold 1.8V           |                                  | switches in and out,<br>$V_{CC} = 2.6V/3.3V/5.5V$                                                              | FBSEL falling  | 0.08                      |     |                           | V     |

|                                      |                                  | Where 2.5V feedback                                                                                            | FBSEL rising   |                           |     | V <sub>CC</sub> -<br>0.08 |       |

| FBSEL Input Threshold 2.5V           |                                  | switches in and out,<br>$V_{CC} = 2.6V/3.3V/5.5V$                                                              | FBSEL falling  | V <sub>CC</sub> -<br>0.22 |     |                           | V     |

| FBSEL Input Current Low              | I <sub>LOW_</sub><br>FBSEL       | FBSEL = GND                                                                                                    |                | -50                       |     |                           | μA    |

| FBSEL Input Current High             | I <sub>HIGH</sub> _<br>FBSEL     | FBSEL = V <sub>CC</sub>                                                                                        |                |                           |     | 50                        | μA    |

| CTL1/CTL2                            |                                  |                                                                                                                |                |                           |     |                           |       |

| CTL 1/CTL 2 Input Threshold VIL_CTL_ |                                  | $V_{IN} = 2.6V$ to 5.5V                                                                                        |                | 0.4                       |     |                           | V     |

| CTL1/CTL2 Input Threshold            | VIH_CTL_                         | $V_{\rm IN} = 2.0V \ 10 \ 5.5V$                                                                                |                |                           |     | 1.6                       | v     |

| CTL1/CTL2 Input Current              | IIL_CTL_                         | $V_{CTL1}$ or $V_{CTL2} = 0$ or 5.5V, $V_{IN} = 5.5V$                                                          |                | -1                        |     | +1                        | μA    |

|                                      | IIH_CTL_                         |                                                                                                                | v, vin = 5.5v  | -1                        |     | +1                        | μΑ    |

| Soft-Start Period                    |                                  | Time required for output t                                                                                     | o ramp up      | 2.9                       |     | 4.5                       | ms    |

| SYNC                                 |                                  |                                                                                                                |                |                           |     |                           |       |

| SYNC Capture Range                   |                                  | $V_{IN} = 2.6V$ to 5.5V                                                                                        |                | 0.4                       |     | 1.2                       | MHz   |

| SYNC Pulse Width                     |                                  | $V_{IN} = 2.6V \text{ to } 5.5V$                                                                               |                | 250                       |     |                           | ns    |

| SYNC Input Threshold                 | VIL_SYNC                         | V <sub>IN</sub> = 2.6V to 5.5V                                                                                 |                | 0.4                       |     |                           | v     |

| Since input mieshold                 | VIH_SYNC                         | VIN - 2.0V 10 3.3V                                                                                             |                |                           |     | 1.6                       | v     |

| SYNC Input Current                   | I <sub>IL,</sub> I <sub>IH</sub> | $V_{SYNC} = 0 \text{ or } 5.5V, V_{IN} = 1$                                                                    | 5.5V           | -1                        |     | +1                        | μA    |

| SYNCOUT                              |                                  |                                                                                                                |                |                           |     |                           |       |

| SYNCOUT Frequency Range              | <b>f</b> SYNCOUT                 | $V_{CC} = 2.6V \text{ to } 5.5V$                                                                               |                | 0.4                       |     | 1.2                       | MHz   |

|                                      | V <sub>OH</sub> _<br>SYNCOUT     |                                                                                                                | 2 6\/ to 5 5\/ | V <sub>CC</sub> -<br>0.4  |     |                           | V     |

| SYNCOUT Output Voltage               | V <sub>OL</sub> _<br>SYNCOUT     | ISYNCOUT = ±1mA, VCC =                                                                                         | 2.00 10 0.00   |                           |     | 0.4                       | V     |

Note 2: Specifications to -40°C are guaranteed by design, not production tested.

Note 3: When connected together, the LX output is designed to provide 6A RMS current.

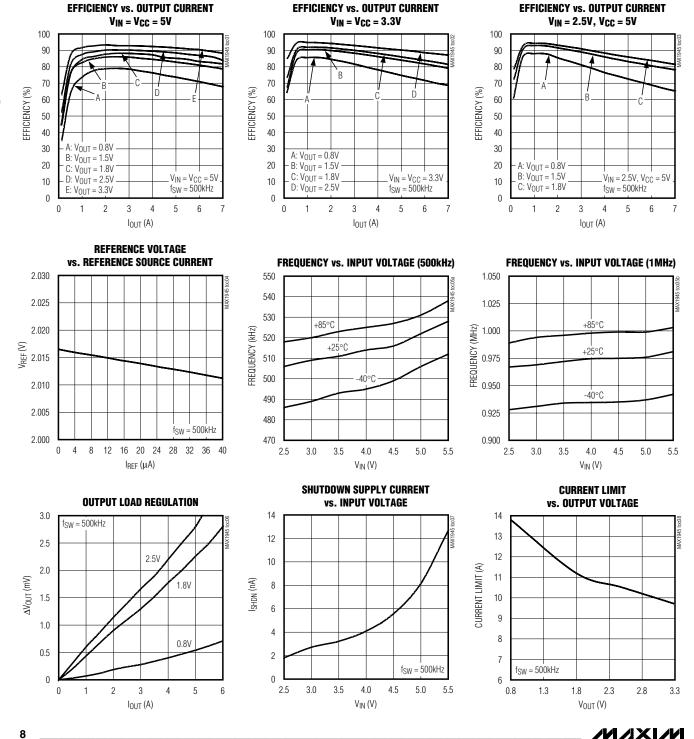

$(V_{IN} = V_{CC} = 5V, V_{OUT} = 1.8V, I_{OUT} = 6A, f_{SW} = 500 \text{kHz}, V_{DD} = V_{CC}$ , and  $T_A = +25^{\circ}\text{C}$ , unless otherwise noted.)

**Typical Operating Characteristics**

MAX1945R/MAX1945S

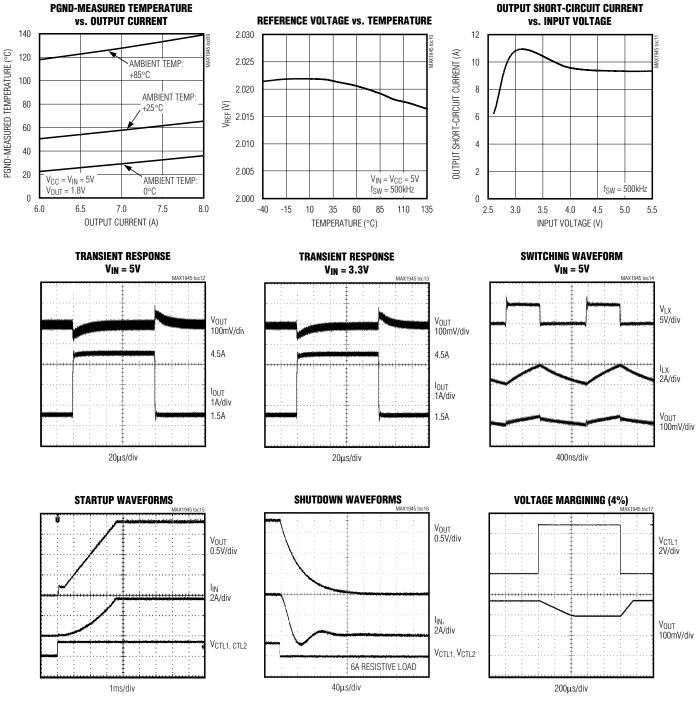

### **Typical Operating Characteristics (continued)**

( $V_{IN} = V_{CC} = 5V$ ,  $V_{OUT} = 1.8V$ ,  $I_{OUT} = 6A$ ,  $f_{SW} = 500$ kHz,  $V_{DD} = V_{CC}$ , and  $T_A = +25^{\circ}$ C, unless otherwise noted.)

MAX1945R/MAX1945S

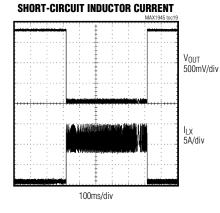

### **Typical Operating Characteristics (continued)**

$(V_{IN} = V_{CC} = 5V, V_{OUT} = 1.8V, I_{OUT} = 6A, f_{SW} = 500kHz, V_{DD} = V_{CC}$ , and  $T_A = +25^{\circ}C$ , unless otherwise noted.)

# VOLTAGE MARGINING (9%) MX11945 toc18 VCTL1 2V/div VCTL1 2V/div Vout 200mV/div 400µs/div

# **Pin Description**

| PIN                              | NAME            | FUNCTION                                                                                                                                                                                                                                                  |

|----------------------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                                | BST             | Bootstrap Voltage. High-side driver supply input. Connect a 0.1µF capacitor from BST to LX. Connect a Schottky diode from IN to BST. A 1N4148 diode can be used for 5V input to reduce cost.                                                              |

| 2                                | V <sub>DD</sub> | Low-Side Driver Supply Voltage                                                                                                                                                                                                                            |

| 3, 5, 7, 9,<br>20, 22, 24,<br>26 | LX              | Inductor Connection. Connect an inductor between LX and the regulator output. Connect all LX pins together close to the device.                                                                                                                           |

| 4, 6, 8, 10                      | IN              | Power-Supply Voltage. Input voltage ranges from 2.6V to 5.5V. Bypass with 3 x 22µF ceramic capacitors in parallel to PGND (see the <i>Input Capacitor Selection</i> section).                                                                             |

| 11                               | V <sub>CC</sub> | Supply-Voltage Input. $V_{CC}$ powers the device. Connect a $10\Omega$ resistor from IN to $V_{CC}.$ Bypass $V_{CC}$ to GND with 0.1µF.                                                                                                                   |

| 12                               | GND             | Analog Ground                                                                                                                                                                                                                                             |

| 13                               | REF             | Reference. Bypass REF with 0.22 $\mu$ F capacitor to GND. REF tracks the soft-start ramp voltage margining and is pulled to GND when the output shuts down.                                                                                               |

| 14                               | COMP            | Regulator Compensation. Connect a series RC network from COMP to GND. COMP is pulled to GND when the output shuts down (see the <i>Compensation Design</i> section).                                                                                      |

| 15                               | FB              | Feedback Input. When FBSEL = High-Z, use an external resistor divider from the output to set the voltage from 0.8V to 85% of $V_{IN}$ . Connect FB to the output for regulation to 1.8V when FBSEL = 0, or for regulation to 2.5V when FBSEL = $V_{CC}$ . |

| 16                               | FBSEL           | Feedback Select Input. The device regulates to an output of 0.8V when FBSEL is left unconnected. The device regulates to an output of 1.8V when FBSEL = GND and regulates to an output of 2.5V when FBSEL = $V_{CC}$ .                                    |

| 17                               | SYNC            | Synchronization/Frequency Select. Connect SYNC to GND for 500kHz operation, to $V_{CC}$ for 1MHz operation, or connect to an external clock at 400kHz to 1.2MHz.                                                                                          |

| 18                               | SYNCOUT         | Synchronization Output. SYNCOUT provides a frequency output synchronized 180 degrees out-of-phase to the operating frequency of the device.                                                                                                               |

# \_Pin Description (continued)

| PIN               | NAME | FUNCTION                                                                                                                                                                                                          |

|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 19, 21, 23,<br>25 | PGND | Power Ground. Connect all PGND together close to the device. Star connect GND to PGND (see the <i>PC Board Layout Considerations</i> section).                                                                    |

| 27                | CTL1 | Output Margining Control Inputs. When CTL1 = CTL2 = GND, the regulator is off. When CTL1 = CTL2 = $V_{CC}$ , the regulator runs at nominal output voltage. When CTL1 = $V_{CC}$ and CTL2 = GND, the output is set |

| 28                | CTL2 | to the margin-low output (-4% or -9%). When $CTL1 = GND$ and $CTL2 = V_{CC}$ , the output is set to the margin-high output (+4% or +9%).                                                                          |

|                   | EP   | Exposed Pad. Connect to PGND to improve power dissipation.                                                                                                                                                        |

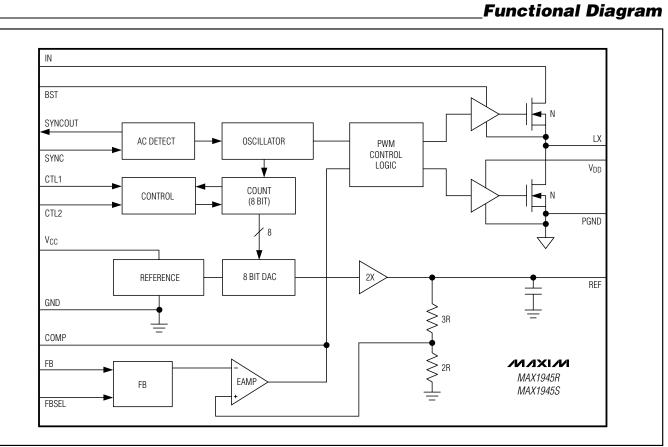

### **Detailed Description**

The MAX1945R/MAX1945S high-efficiency PWM switching regulators deliver up to 6A of output current. The devices operate at a selectable fixed frequency (500kHz or 1MHz) or can be synchronized to an external frequency (400kHz to 1.2MHz). The devices operate from a 2.6V to 5.5V input supply voltage and have a selectable output voltage from 0.8V to 85% of the input voltage, making the MAX1945R/MAX1945S ideal for onboard post-regulation applications. The high switching frequency allows the use of small external components. Internal synchronous rectifiers improve efficiency and eliminate the typical Schottky freewheeling diode. Total output error over load, line, and temperature is less than ±1%.

#### **Controller Function**

The MAX1945R/MAX1945S step-down converters use a PWM current-mode control scheme. A PWM comparator compares the integrated voltage-feedback signal against the sum of the amplified current-sense signal and the slope-compensation ramp. At each rising edge of the internal clock, the internal high-side MOSFET turns on until the PWM comparator trips. During this ontime, current ramps up through the inductor, sourcing current to the output and storing energy in the inductor. The current-mode feedback system regulates the peak inductor current as a function of the output voltage error signal. Because the average inductor current is nearly the same as the peak inductor current (<30% ripple current), the circuit acts as a switch-mode transconductance amplifier.

To preserve inner-loop stability and eliminate inductor staircasing, a slope-compensation ramp is summed into the main PWM comparator. During the off-cycle, the internal high-side N-channel MOSFET turns off, and the internal low-side N-channel turns on. The inductor releases the stored energy as its current ramps down while still providing current to the output. The output capacitor stores charge when the inductor current exceeds the load current and discharges when the inductor current is lower, smoothing the voltage across the load. During an overload condition, when the inductor current exceeds the current limit (see the *Current Limit* section), the highside MOSFET does not turn on at the rising edge of the clock, and the low-side MOSFET remains on to let the inductor current ramp down.

#### **Current Sense**

An internal current-sense amplifier produces a current signal proportional to the voltage generated by the high-side MOSFET on-resistance and the inductor current (R<sub>DS(ON)</sub> × I<sub>LX</sub>). The amplified current-sense signal and the internal slope-compensation signal sum together at the comparator inverting input. The PWM comparator turns off the internal high-side MOSFET when this sum exceeds the COMP voltage from the error amplifier.

#### **Current Limit**

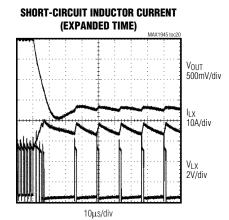

The internal high-side MOSFET has a current limit of 8A (min). If the current flowing out of LX exceeds this limit, the high-side MOSFET turns off and the synchronous rectifier turns on. This lowers the duty cycle and causes the output voltage to droop until the current limit is no longer exceeded. The minimum duty cycle is limited to 10%. A synchronous rectifier current limit of 2A minimum protects the device from current flowing into LX.

When the negative current limit is exceeded, the device turns off the synchronous rectifier, forcing the inductor current to flow through the high-side MOSFET body diode and back to the input, until the beginning of the next cycle, or until the inductor current drops to zero. The MAX1945R/MAX1945S use a pulse-skip mode to prevent overheating during short-circuit output conditions. The device enters pulse-skip mode when the FB voltage drops below 300mV, limiting the current and reducing power dissipation. Normal operation resumes upon removal of the short-circuit condition.

### Soft-Start

The MAX1945R/MAX1945S employs digital soft-start to reduce supply in-rush current during startup conditions. When the device exits undervoltage lockout (UVLO), shutdown mode, or restarts following a thermal-overload event, the digital soft-start circuitry slowly ramps up the voltages at REF and FB (see the *Typical Operating Characteristics*). An internal oscillator sets the soft-start time to 3.7ms (typ). Use a of 0.22µF capacitor (min) to reduce the susceptibility to switching noise.

#### **Undervoltage Lockout (UVLO)**

When  $V_{CC}$  drops below 2.35V, the UVLO circuit inhibits switching. Once  $V_{CC}$  rises above 2.4V, UVLO clears and the soft-start function activates.

#### Bootstrap (BST)

A capacitor connected between BST and LX and a Schottky diode connected from IN to BST generate the gate drive for the internal high-side N-channel MOSFET. When the low-side N-channel MOSFET is on, LX goes to PGND. IN charges the bootstrap capacitor through the Schottky diode. When the low-side N-channel MOSFET turns off and the high side N-channel MOSFET turns on,  $V_{LX}$  goes to  $V_{IN}$ . The Schottky diode prevents the capacitor from discharging into IN.

#### Frequency Select (SYNC)

The MAX1945R/MAX1945S operate in PWM mode with a selectable fixed frequency or synchronized to an external frequency. The devices switch at a frequency of 500kHz when SYNC is connected to ground. The devices switch at 1MHz with SYNC connected to V<sub>CC</sub>. Apply an external frequency of 400kHz to 1.2MHz with 10% to 90% duty cycle at SYNC to synchronize the switching frequency of MAX1945R/MAX1945S.

#### **Output Voltage Select**

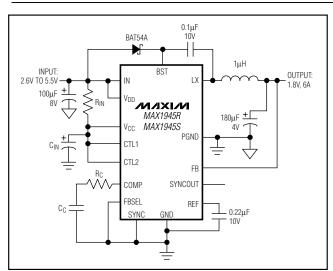

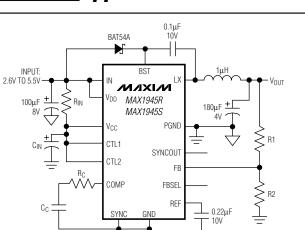

The MAX1945R/MAX1945S feature selectable fixed and adjustable output voltages. With FB connected to the output, the output voltage is 1.8V when FBSEL is at GND and 2.5V when FBSEL is at V<sub>CC</sub> (Figure 1). When FBSEL is floating, connect FB to an external resistor divider from V<sub>OUT</sub> to GND to set the output voltage from 0.8V to 85% of V<sub>IN</sub> (Figure 2). Select R2 in the 1k $\Omega$  to 10k $\Omega$  range. Calculate R1 using the following equation:

$$R1 = R2 \left( \frac{V_{OUT}}{V_{FB}} - 1 \right)$$

where  $V_{FB} = 0.8V$ .

#### Shutdown Mode

Drive CTL1 and CTL2 to ground to shut down the MAX1945R/MAX1945S. In shutdown mode, the internal MOSFETs stop switching and LX goes to high impedance; REF and COMP go to ground.

#### **Voltage Margining**

The MAX1945R/MAX1945S provide selectable voltage margining. The MAX1945R provides  $\pm 4\%$  voltage margining, and the MAX1945S provides  $\pm 9\%$  voltage margining. CTL1 and CTL2 set the voltage margins (Table 1).

#### Table 1. Setting Voltage Margin

|                | CTL1            | CTL2            | V <sub>OUT</sub> |          |  |

|----------------|-----------------|-----------------|------------------|----------|--|

|                | CILI            | CILZ            | MAX1945R         | MAX1945S |  |

|                | 0V              | 0V              | OFF              | OFF      |  |

|                | V <sub>CC</sub> | V <sub>CC</sub> | NOMINAL          | NOMINAL  |  |

| Voltage Margin | Vcc             | 0V              | -4%              | -9%      |  |

|                | 0V              | Vcc             | +4%              | +9%      |  |

#### **Thermal Protection**

Thermal-overload protection limits total power dissipation in the device. When the junction temperature (TJ) exceeds 165°C, a thermal sensor forces the device into shutdown, allowing the die to cool. The thermal sensor turns the device on again after the junction temperature cools by 20°C, causing a pulsed output during continuous overload conditions. The soft-start sequence begins after a thermal-shutdown condition.

#### **Design Procedure**

#### Vcc Decoupling

Because of the high switching frequency and tight output tolerance, decouple V<sub>CC</sub> with 0.1µF capacitor from V<sub>CC</sub> to GND with a 10 $\Omega$  resistor from V<sub>CC</sub> to IN. Place the capacitor as close to VCC as possible.

#### **Inductor Design**

Choose an inductor with the following equation:

L

$$=\frac{V_{OUT} \times (V_{IN} - V_{OUT})}{f_{OSC} \times V_{IN} \times LIR \times I_{OUT(MAX)}}$$

where LIR is the ratio of the inductor ripple current to average continuous current at a minimum duty cycle. Choose LIR between 20% to 40% of the maximum load current for best performance and stability.

Use a low-loss inductor with the lowest possible DC resistance that fits in the allotted dimensions. Ferrite core types are often the best choice for performance. With any core material the core must be large enough not to saturate at the peak inductor current (IPEAK).

$$I_{\text{PEAK}} = \left(1 + \frac{\text{LIR}}{2}\right) I_{\text{OUT}(\text{MAX})}$$

Example:

$V_{IN} = 3.3V$   $V_{OUT} = 1.8V$   $f_{OSC} = 500 \text{kHz}$   $I_{OUT(MAX)} = 6\text{A}$  LIR = 30% $L = 1\mu\text{H and IPEAK} = 6.9\text{A}$

#### **Output Capacitor Selection**

The key selection parameters for the output capacitor are capacitance, ESR, ESL, and voltage rating requirements. These affect the overall stability, output ripple voltage, and transient response of the DC-DC converter. The output ripple occurs because of variations in the charge stored in the output capacitor, the voltage drop due to the capacitor's ESR, and the voltage drop due to the capacitor's ESL. Calculate the output voltage ripple due to the output capacitance, ESR, and ESL as:

$V_{RIPPLE} = V_{RIPPLE(C)} + V_{RIPPLE(ESR)} + V_{RIPPLE(ESL)}$

where the output ripple due to output capacitance, ESR, and ESL are:

$$\label{eq:VRIPPLE(C)} \begin{split} &\mathsf{VRIPPLE(C)} = \mathsf{IP}\text{-P}/(8\times\mathsf{COUT}\times\mathsf{fSW}), \ \mathsf{VRIPPLE(ESR)} = \mathsf{IP}\text{-P}\times\\ &\mathsf{ESR}\\ \\ &\mathsf{VRIPPLE(ESL)} = (\mathsf{IP}\text{-P}/\mathsf{tON})\times\mathsf{ESL} \ \mathsf{or} \ (\mathsf{IP}\text{-P}/\mathsf{tOFF})\times\mathsf{ESL}, \end{split}$$

whichever is greater

The peak inductor current (IP-P) is:

$$I_{P-P} = ((V_{IN} - V_{OUT})/(f_{SW} \times L)) \times (V_{OUT}/V_{IN})$$

Example:

$V_{IN} = 3.3V$  $V_{OUT} = 1.8V$  $f_{OSC} = 500 \text{kHz}$

$$\begin{split} &\text{IOUT(MAX)} = 6A\\ &\text{LIR} = 30\%\\ &\text{L} = 1\mu\text{H}\\ &\text{COUT} = 180\mu\text{F}\\ &\text{ESR(OUTPUT CAPACITOR)} = 30m\Omega\\ &\text{ESL(OUTPUT CAPACITOR)} = 2.5n\text{H}\\ &\text{VRIPPLE(C)} = 2m\text{V}\\ &\text{VRIPPLE(ESR)} = 45m\text{V}\\ &\text{VRIPPLE(ESL)} = 4m\text{V}\\ &\text{VRIPPLE} = 51m\text{V} \end{split}$$

Use these equations for initial capacitor selection. Determine final values by testing a prototype or an evaluation circuit. A smaller ripple current results in less output voltage ripple. Because the inductor ripple current is a factor of the inductor value, the output voltage ripple decreases with a larger inductance. Use ceramic capacitors for low ESR and low ESL at the switching frequency of the converter. The low ESL of ceramic capacitors makes ripple voltages negligible. Load transient response depends on the selected output. During a load transient, the output instantly changes by ESR x ILOAD. Before the controller can respond, the output deviates further, depending on the inductor and output capacitor values. After a short time (see the Transient Response graphs in the Typical Operating Characteristics), the controller responds by regulating the output voltage back to its predetermined value. The controller response time depends on the closed-loop bandwidth.

A higher bandwidth yields a faster response time, preventing the output from deviating further from its regulating value.

#### **Input Capacitor Selection**

The input capacitor reduces the current peaks drawn from the input power supply and reduces switching noise in the IC. The impedance of the input capacitor at the switching frequency should be less than that of the input source so that high-frequency switching currents do not pass through the input source but instead are shunted through the input capacitor. A high source impedance requires larger input capacitance. The input capacitor must meet the ripple current requirement imposed by the switching currents. The RMS input ripple current is given by:

$$I_{\text{RIPPLE}} = I_{\text{LOAD}} \times \left( \frac{\sqrt{V_{\text{OUT}} \times (V_{\text{IN}} - V_{\text{OUT}})}}{V_{\text{IN}}} \right)$$

where IRIPPLE is the input RMS ripple current.

#### **Compensation Design**

The double pole formed by the inductor and the output capacitor of most voltage-mode controllers introduces a large phase shift, which requires an elaborate compensation network to stabilize the control loop. The MAX1945R/MAX1945S controllers utilize a current-mode control scheme that regulates the output voltage by forcing the required current through the external inductor, eliminating the double pole caused by the inductor and output capacitor, and greatly simplifying the compensation network. A simple Type 1 compensation with a single compensation resistor (R<sub>C</sub>) and compensation capacitor (C<sub>C</sub>) creates a stable and high bandwidth loop (Figure 1).

An internal transconductance error amplifier compensates the control loop. Connect a series resistor and capacitor between COMP (the output of the error amplifier) and GND, to form a pole-zero pair. The external inductor, internal current-sense circuitry, output capacitor, and external compensation circuit determine the loop-system stability. Choose the inductor and output capacitor based on performance, size, and cost. Additionally, select the compensation resistor and capacitor to optimize control-loop stability. The component values shown in the typical application circuit yield stable operation over a broad range of input-to-output voltages.

Compensating the voltage feedback loop depends on the type of output capacitors used. Common capacitors for output filtering: ceramic capacitors, polymer capacitors such as POSCAPs and SPCAPs, and electrolytic capacitors. Use either ceramic or polymer capacitors. Use polymer capacitors as the output capacitor when selecting 500kHz operation. At 500kHz switching, the voltage feedback loop is slower (about 50kHz to 60kHz) when compared to 1MHz switching. Therefore, a polymer capacitor's high capacitance for a given footprint improves the output response during a step load change. Because of its relative low ESR frequencies (about 20kHz to 80kHz), use Type 2 compensation. The additional high-frequency pole introduced in Type 2 compensation offsets the ESR zero introduced by the polymer capacitors to provide continuous attenuation above the ESR zero frequencies of the polymer capacitors. However, the presence of the parasitic capacitance at COMP and the high output impedance of the error amplifier already provide the required attenuation above the ESR frequencies. The following steps outline the design process of compensating the MAX1945 with polymer output capacitors with the components in the application circuits Figures 1 and 2.

$$\label{eq:generalized_response} \begin{split} \text{Regulator DC Gain:} \\ \text{G}_{\text{DC}} = \Delta \text{V}_{\text{OUT}} / \Delta \text{V}_{\text{COMP}} = \text{gmc} \times \text{R}_{\text{OUT}} \end{split}$$

Load Impedance Pole Frequency:  $f_{PLOAD} = 1/(2 \times \pi \times C_{OUT} \times (R_{OUT} + R_{ESR}))$

Load Impedance Zero Frequency: fzESR =  $1/(2 \times \pi \times C_{OUT} \times R_{ESR})$

where ROUT = VOUT/IOUT(MAX), and gmc = 18.2S.

The feedback divider has a gain of GFB = VFB/VOUT, where VFB = 0.8V. The transconductance error amplifier has a DC gain, GEA(DC), of 70dB. The compensation capacitor, C<sub>C</sub>, and the output resistance of the error amplifier, R<sub>OEA</sub> (20M $\Omega$ ), set the dominant pole. C<sub>C</sub> and R<sub>C</sub> set a compensation zero. Calculate the dominant pole frequency as:

$$fp = 1/(2\pi \times C_C \times R_{OEA})$$

Determine the compensation zero frequency as:

$$f_{ZEA} = 1/(2\pi \times C_C \times R_C)$$

For best stability and response performance, set the closed-loop unity-gain frequency much higher than the load-impedance pole frequency. The closed-loop unity-gain crossover frequency must be less than one-fifth of the switching frequency. Set the crossover frequency to 10% to 15% of the switching frequency. The loop-gain equation at unity-gain frequency, fc, is given by:

$$G_{EA} \times G_{DC} \times (f_{PLOAD}/f_C) \times (V_{FB}/V_{OUT}) = 1$$

where  $G_{EA} = gm_{EA} \times R_C$ , and  $gm_{EA} = 50\mu S$ , the transconductance of the voltage-error amplifier. Calculate  $R_C$  as:

$R_{C} = (V_{OUT} \times f_{C})/(g_{MEA} \times V_{FBX} \times G_{DC} \times f_{PLOAD})$

Set the error-amplifier compensation zero formed by R<sub>C</sub> and C<sub>C</sub> equal to the load-impedance pole frequency, fPLOAD, at maximum load. Calculate C<sub>C</sub> as:

#### $C_C = (C_{OUT} \times R_{OUT})/R_C$

#### 500kHz Switching

The following design example is for the application circuit shown in Figures 1 and 2:

$V_{OUT} = 1.8V$

IOUT(MAX) = 6A

$C_{OUT} = 180 \mu F$

$R_{ESR} = 0.04\Omega$

$gm_{EA} = 50 \mu s$

gmc = 18.2s

fswitch = 500kHz

$R_{OUT} = V_{OUT}/I_{OUT(MAX)} = 1.8V/6 A = 0.3\Omega$

fpDC =  $1/(2\pi \times C_{OUT} \times (R_{OUT} + R_{ESR})) = 1/(2\pi \times 180 \times 10^{-6} \times (0.3 + 0.04)) = 2.6 \text{kHz}.$

$f_{ZESR} = 1/(2\pi \times C_{OUT} R_{ESR}) = 1/(2\pi \times 180 \times 10^{-6} \times 0.04) = 22.1 \text{ kHz}.$

Pick the closed-loop unity-gain crossover frequency ( $f_c$ ) at 60kHz. Determine the switching regulator DC gain:

$G_{DC} = g_{MC} \times R_{OUT} = 18.2 \times 0.3 = 5.46$

then:

$\begin{array}{l} \mathsf{R}_{\mathsf{C}} = (\mathsf{V}_{\mathsf{OUT}} \times \mathsf{f}_{\mathsf{C}}) / (\mathsf{gm}_{\mathsf{EA}} \times \mathsf{V}_{\mathsf{FB}} \times \mathsf{G}_{\mathsf{DC}} \times \mathsf{fp}_{\mathsf{LOAD}}) = \\ (1.8 \times 60 \text{kHz}) / (50 \times 10^{-6} \times 0.8 \times 5.46 \times 2.6 \text{kHz}) \approx 190 \text{k}\Omega \\ (1\%), \, \mathsf{choose} \; \mathsf{R}_{\mathsf{C}} = 180 \text{k}\Omega, \; 1\% \end{array}$

$C_{C} = (C_{OUT} \times (R_{OUT} + R_{ESR}))/R_{C} = (180 \text{uF} \times (0.3 + 0.04))/180 \text{k}\Omega \approx 340 \text{pF}, \text{ choose } C_{C} = 330 \text{pF}, 10\%$

Table 2 shows the recommended values for  $R_C$  and  $C_C$  for different output voltages.

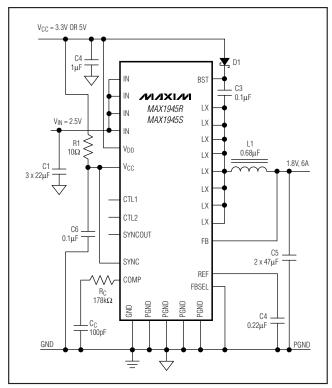

#### 1MHz Switching

Following procedure outlines the compensation process of the MAX1945 for 1MHz operation with all ceramic output capacitors (Figure 3). The basic regulator loop consists of a power modulator, an output-feedback divider, and an error amplifier. The switching regulator has a DC gain set by gmc  $\times$  R<sub>OUT</sub>, where gmc is the transconductance from the output voltage of the error amplifier to the output inductor current. The load impedance of the switching modulator consists of a pole-zero pair set by R<sub>OUT</sub>, the output capacitor (C<sub>OUT</sub>), and its ESR. The following equations define the power train of the switching regulator:

Regulator DC Gain:

$G_{DC} = \Delta V_{OUT} / \Delta V_{COMP} = gmc \times R_{OUT}$

Load-Impedance Pole Frequency:  $f_{PLOAD} = 1/(2 \times \pi \times C_{OUT} \times (R_{OUT} + R_{ESR}))$

Load-Impedance Zero Frequency:

$f_{ZESR} = 1/(2 \times \pi \times C_{OUT} \times R_{ESR})$

where, R<sub>OUT</sub> = V<sub>OUT</sub>/I<sub>OUT</sub>(MAX), and gmc = 18.2. The feedback divider has a gain of GFB = V<sub>FB</sub>/V<sub>OUT</sub>, where V<sub>FB</sub> is equal to 0.8V. The transconductance error amplifier has a DC gain, G<sub>EA</sub>(DC), of 70dB. The compensation capacitor, C<sub>C</sub>, and the output resistance of the error amplifier, R<sub>OEA</sub> (20M $\Omega$ ), set the dominant pole. C<sub>C</sub> and R<sub>C</sub> set a compensation zero. Calculate the dominant pole frequency as:

$$fp_{EA} = 1/(2\pi \times C_C \times R_{OEA})$$

Determine the compensation zero frequency as:

$$f_{ZEA} = 1/(2\pi \times C_C \times R_C)$$

For best stability and response performance, set the closed-loop unity-gain frequency much higher than the load impedance pole frequency. In addition, set the closed-loop unity-gain crossover frequency less than one-fifth of the switching frequency. However, the maxi-

#### Table 2. Compensation Values for Output Voltages (500kHz)

| VOUT (V) | 0.8           | 1.2           | 1.8           | 2.5           | 3.3           |

|----------|---------------|---------------|---------------|---------------|---------------|

| RC       | 110k $\Omega$ | 147k $\Omega$ | 180k $\Omega$ | 287k $\Omega$ | $365 k\Omega$ |

| CC       | 330pF         | 330pF         | 330pF         | 220pF         | 220pF         |

### Table 3. Compensation Values for Output Voltages (1MHz)

| VOUT (V)             | 0.8           | 1.2   | 1.8           | 2.2           | 3.3   |

|----------------------|---------------|-------|---------------|---------------|-------|